³���ŤΥޥ����� CD70-SC(����1)

��4ǯ�����֤��Ƥ�������������ȯɽ�Ǥ���(�Ĥ��SDVIA��FW6400GX��������)��

����������

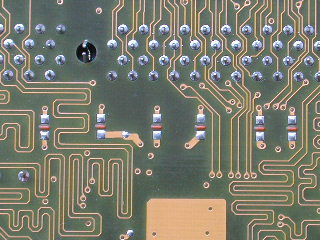

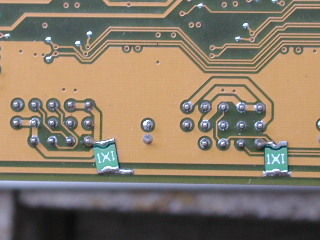

�����Υޥ����ϥܡ��ɤ��ǥ������⤢�뤬�����������ۤɥ�����Ų�¿��������Ū���������ɮ�ԤǤ��������ʤ��ۤ�¿��(����66�ܤϤ��������ǹ�)���ȤƤ�쵤������̵�������Ӥ�ᥤ��ʳ��Ͼ�ά��

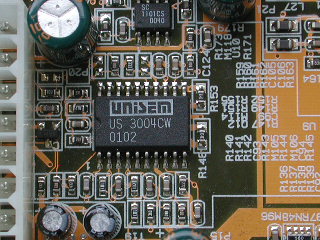

VRM����ȥ����顧US3004CW

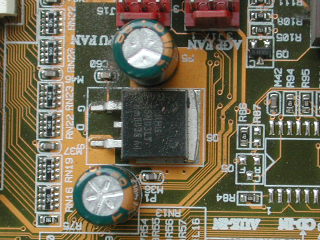

Vmem����ȥ����顧SC1101CS

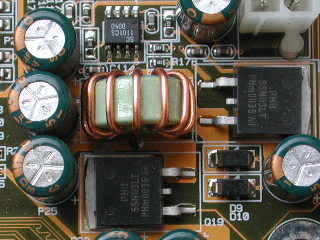

�岼FET��PHB55N03LT

���ϥ����������T50-52D[#17,5t]

���ϥ����������T50-52D[#17,8t]

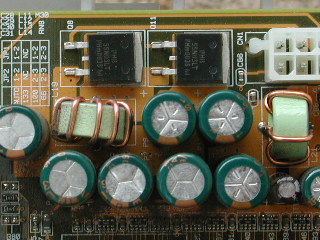

Vcore���ϥ���ǥ�TEAPO[SC]1500��F10V��3

Vcore���ϥ���ǥ�TEAPO[SC]1500��F6.3V��5

L21������ǥ�TEAPO[SC]1000��F6.3V

����¾DC��TEAPO[SC]1000��F6.3V��24

����¾DC��TEAPO[SEK]100��F16V��9

����¾DC��TEAPO[SX]10��F25V��24

DRAM�����å��Хåե���IMI B9847AY

�����å������ͥ졼����IMI C9846AY

������Ū����̣�Ƿ��¤Ǥ��롣������OEM��ͺDFI�ȸ��ä��꤫�����åפ���ʪ�ʤΤ��¤��Ĥ뤬�ġ����餯DDR��������������ʤ���������������DDR����⥸�塼�뼫�Τ��ʼ�����Ф���������

���ȷ���¬

�����Υޥ����ϥƥ��ȡ���¬������(2006ǯ)�Ǥϡ�����¬�ޥ�����ǺǤ������������å����ȷ��Ǥ��ä�������ϥǥХ������ϩ�߷פ����Ǥʤ������ĥѥ����ǥ���������ޤ९��ƥ�����ʥХ�ξ�ˤ�������������Ω�Ĥ�Ρ��Υ��ϥ��ξ��ʤ��Ԥ�������äȷ����ƽ����褦�ʤ�ΤǤϤʤ����ȷ��ϥ���ǥ��������Ƥ���ΤǺ���ϷǺܤ��ʤ���

��US3004CW��ɸ�ॹ���å����ȿ���220(��30)kHz���������Υޥ����Ǥϵ�����ǤϤ��뤬���¤˶ᤤ193.6kHz����(�Ķ��˰ͤ�)�Ǥ��ä���Ct��Ĵ�٤��櫓�ǤϤʤ������տ�Ū�����μ��ȿ������ꤷ�Ƥ���Ȼפ��롣

��ư�����Ƥߤ�

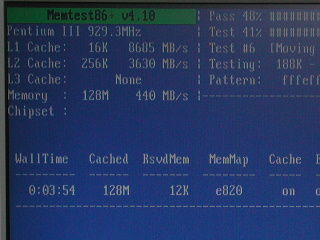

��DDR���������ȸ����櫓�ǤϤʤ��������Ĥ��ꥯ���å��ι⤤SL44J��ܤ��Ƶ�ư���Ƥߤ롣�����KINGMAX�ν���128MB����Ѥ�����MEMTEST86+��®�٤Ϥ������̤�Ǥ��ʤ�®��������ʤ������Υ�������ȸ߳Ѱʾ���廊�롣����ƥ뤬�Ĥޤ�ʤ����Ϥ修ǰ����P6��DDR-SDRAM�Υ��åץ��åȤ�Ф��ʤ��ä��Τ��ˤ��ޤ�롣�դ�AMD�����������ĤäƤ���ΤϤ��Τ����ȸ����ʤ���̵��������ƥ�ν�������ǡ����ޤ줿�Ƥ�Athlon���ֻҤ��ʳ����٤���Ƥ������������顣

�㤳��®�ٶ��դΥ饤�Х뤿����

582MB/s:DHD0900AMT1B(1193MHz)AMD761(133)

440MB/s:SL44J(929.3MHz)�����ޥ���AP266(133)

378MB/s:A0800AMT3B(960.0MHz)MAGiK1(120)

360MB/s:SL44J(930.2MHz)i815E(133)

(���������ޥ����ϥǥե�����������¾�Ϻ�®����)

��®��Ū�ˤ�˫�AP266����������������ΰ�����ŷ�����ʤ���DRD-RAM��Ʊ���ʾ�ʤΤdzи礷�������ɤ����ޤ����ʤ�쥢�ʥ��åץ��åȤʤΤǡ�������ɤߤ��������������뵡��Ϥ������ʤ����������ɡ�

��������

��VRM�����Ǥʤ�����Ū�˹��ѡ��Ĥ������Ȥ��Ƥ��餺���ȷ�������������DFI���߷ס���¤���Ѥ����߽Ф�����Τȸ����롣���λ���Υޥ����ϡ��ɤ��Τɤ�ʥ��åץ��åȤ�ȤäƤ������θ�������̤˽ФƤ��ޤ����������ˤȤäƤϤȤƤ����������ä����Ƕ�ΤϤɤ��̵���������ʤ���

������Ϥ��Τ��Ȥ��������Ϯ�äƤߤ뤫���֤��뤫�Ĥ��������ʤ�¿������ť�²������ʤ�����ǯ�¤ʷ��֤˼�����������������褽����̵���ʡ��������ʡ������ʤ�Ȥ�������ޥ�����������ʤμ�̿��ͤ���Ȥ����������ʤ����㤤���ʤ�������ɡ��ä�5~6�դΥ��ӥ���Ϥ⤦��̿����Ƥ���ϥ������Ǥ⤳�������ʤ�Ȳ����뵤�������ʤ��ʡġ�

��4ǯ�����֤��Ƥ�������������ȯɽ�Ǥ���(�Ĥ��SDVIA��FW6400GX��������)��

����������

�����Υޥ����ϥܡ��ɤ��ǥ������⤢�뤬�����������ۤɥ�����Ų�¿��������Ū���������ɮ�ԤǤ��������ʤ��ۤ�¿��(����66�ܤϤ��������ǹ�)���ȤƤ�쵤������̵�������Ӥ�ᥤ��ʳ��Ͼ�ά��

VRM����ȥ����顧US3004CW

Vmem����ȥ����顧SC1101CS

�岼FET��PHB55N03LT

���ϥ����������T50-52D[#17,5t]

���ϥ����������T50-52D[#17,8t]

Vcore���ϥ���ǥ�TEAPO[SC]1500��F10V��3

Vcore���ϥ���ǥ�TEAPO[SC]1500��F6.3V��5

L21������ǥ�TEAPO[SC]1000��F6.3V

����¾DC��TEAPO[SC]1000��F6.3V��24

����¾DC��TEAPO[SEK]100��F16V��9

����¾DC��TEAPO[SX]10��F25V��24

DRAM�����å��Хåե���IMI B9847AY

�����å������ͥ졼����IMI C9846AY

������Ū����̣�Ƿ��¤Ǥ��롣������OEM��ͺDFI�ȸ��ä��꤫�����åפ���ʪ�ʤΤ��¤��Ĥ뤬�ġ����餯DDR��������������ʤ���������������DDR����⥸�塼�뼫�Τ��ʼ�����Ф���������

���ȷ���¬

�����Υޥ����ϥƥ��ȡ���¬������(2006ǯ)�Ǥϡ�����¬�ޥ�����ǺǤ������������å����ȷ��Ǥ��ä�������ϥǥХ������ϩ�߷פ����Ǥʤ������ĥѥ����ǥ���������ޤ९��ƥ�����ʥХ�ξ�ˤ�������������Ω�Ĥ�Ρ��Υ��ϥ��ξ��ʤ��Ԥ�������äȷ����ƽ����褦�ʤ�ΤǤϤʤ����ȷ��ϥ���ǥ��������Ƥ���ΤǺ���ϷǺܤ��ʤ���

��US3004CW��ɸ�ॹ���å����ȿ���220(��30)kHz���������Υޥ����Ǥϵ�����ǤϤ��뤬���¤˶ᤤ193.6kHz����(�Ķ��˰ͤ�)�Ǥ��ä���Ct��Ĵ�٤��櫓�ǤϤʤ������տ�Ū�����μ��ȿ������ꤷ�Ƥ���Ȼפ��롣

��ư�����Ƥߤ�

��DDR���������ȸ����櫓�ǤϤʤ��������Ĥ��ꥯ���å��ι⤤SL44J��ܤ��Ƶ�ư���Ƥߤ롣�����KINGMAX�ν���128MB����Ѥ�����MEMTEST86+��®�٤Ϥ������̤�Ǥ��ʤ�®��������ʤ������Υ�������ȸ߳Ѱʾ���廊�롣����ƥ뤬�Ĥޤ�ʤ����Ϥ修ǰ����P6��DDR-SDRAM�Υ��åץ��åȤ�Ф��ʤ��ä��Τ��ˤ��ޤ�롣�դ�AMD�����������ĤäƤ���ΤϤ��Τ����ȸ����ʤ���̵��������ƥ�ν�������ǡ����ޤ줿�Ƥ�Athlon���ֻҤ��ʳ����٤���Ƥ������������顣

�㤳��®�ٶ��դΥ饤�Х뤿����

582MB/s:DHD0900AMT1B(1193MHz)AMD761(133)

440MB/s:SL44J(929.3MHz)�����ޥ���AP266(133)

378MB/s:A0800AMT3B(960.0MHz)MAGiK1(120)

360MB/s:SL44J(930.2MHz)i815E(133)

(���������ޥ����ϥǥե�����������¾�Ϻ�®����)

��®��Ū�ˤ�˫�AP266����������������ΰ�����ŷ�����ʤ���DRD-RAM��Ʊ���ʾ�ʤΤdzи礷�������ɤ����ޤ����ʤ�쥢�ʥ��åץ��åȤʤΤǡ�������ɤߤ��������������뵡��Ϥ������ʤ����������ɡ�

��������

��VRM�����Ǥʤ�����Ū�˹��ѡ��Ĥ������Ȥ��Ƥ��餺���ȷ�������������DFI���߷ס���¤���Ѥ����߽Ф�����Τȸ����롣���λ���Υޥ����ϡ��ɤ��Τɤ�ʥ��åץ��åȤ�ȤäƤ������θ�������̤˽ФƤ��ޤ����������ˤȤäƤϤȤƤ����������ä����Ƕ�ΤϤɤ��̵���������ʤ���

������Ϥ��Τ��Ȥ��������Ϯ�äƤߤ뤫���֤��뤫�Ĥ��������ʤ�¿������ť�²������ʤ�����ǯ�¤ʷ��֤˼�����������������褽����̵���ʡ��������ʡ������ʤ�Ȥ�������ޥ�����������ʤμ�̿��ͤ���Ȥ����������ʤ����㤤���ʤ�������ɡ��ä�5~6�դΥ��ӥ���Ϥ⤦��̿����Ƥ���ϥ������Ǥ⤳�������ʤ�Ȳ����뵤�������ʤ��ʡġ�